薄层板作为PDN设计的嵌入式电容

配电网(pdn)的功能是为电子设备提供清洁电源,这是电源完整性的强制性要求,并提供可靠的信号返回路径,作为信号完整性[1]的选项。

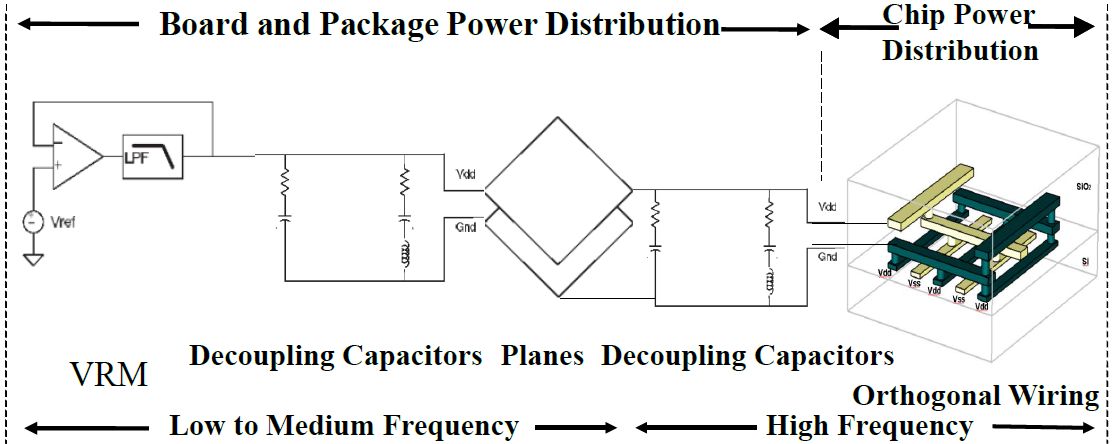

电子设备中的清洁电源分配要求系统设计能够充分利用板载、封装和片上功能。板载电容的功率解耦最适用于低频,中频功率解耦最适用于封装电容,而片上电容满足高频功率解耦(见图1)。

图1所示。功率分配模型-在封装中使用靠近IC的平面电容器,可降低回路电感和整体电路阻抗[2]

在电信和网络行业的配电应用需要越来越密集的集成电路设计,更小的芯片几何形状和更高的设备速度,这推动了微处理器从PDN提取的电流。功率耗散的增加对降噪提出了严格的要求,为了降低噪声源,需要在PDN上增加更多的去耦电容。然而,由于电感的增加,它会引起路由问题并改变电容器的预期性能。

使用薄层和非常薄的铜箔层板作为内嵌电容(即一对功率/接地层对)是一种消除电路板上许多去耦电容的方法——不是因为薄层板的电容增加,而是因为它的电感[3]较低。

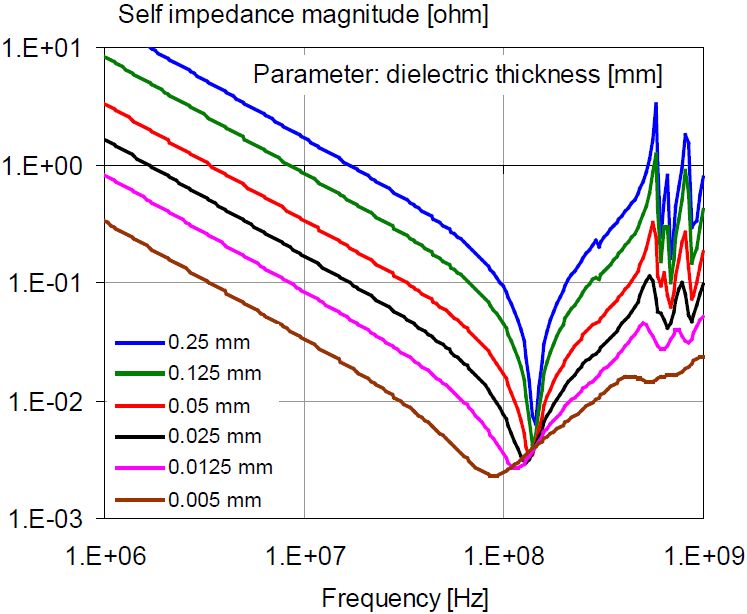

图2中的阻抗图显示了不同介质厚度的正方形对平面的阻抗幅值。当0.25mm (10-mil, 250µm)平面分离时,共振频率处的阻抗波动较大,当厚度降到25µm或以下时,阻抗明显减小。PDN阻抗与层压厚度近似成正比。当层合板变薄时,可以实现模态共振的抑制。

图2。不同层合板厚度的自阻抗大小——薄层合板通过其电感与平面间距[4]成比例,有助于降低高频阻抗

Interra®HK04薄层压板

杜邦公司提供InterraHK04薄层作为嵌入电容。它们可以用作PDN设计选项之一。25 μ m和12 μ m介质层合板的使用都显示了各自的优点,例如,减少了去耦电容的数量,腾出了设计空间,降低了噪音,从而提高了板的可靠性。

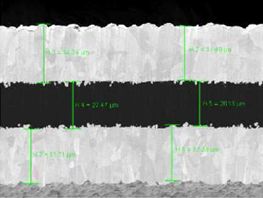

Interra HK04在频率、偏置电压和温度范围内提供卓越的电容稳定性。电介质的均匀性与刚性板的制造工艺相兼容,表现出优异的耐化学性,特别是在干膜工艺中,并且不易发生分层。此外,由于其高柔韧性,层压板可以在不影响机械性能的情况下制作得更薄,这改善了制造商的操作,提高了产量。图3为25µm HK04J薄膜的显微切片。

图3。Interra HK04J显微切片-铜平面之间的全聚酰亚胺提供介质膜强度,以实现机械可靠性和电气性能。

最新加入我们的Interra HK04家族是HK04M,进一步改进了我们的长期Interra HK04J。这种新型层压板的主要特点包括:

- 高模量聚酰亚胺芯,更好地处理0.5 mil介质

- 优化低调铜的选择

- 在内层过程中帮助产量的能力

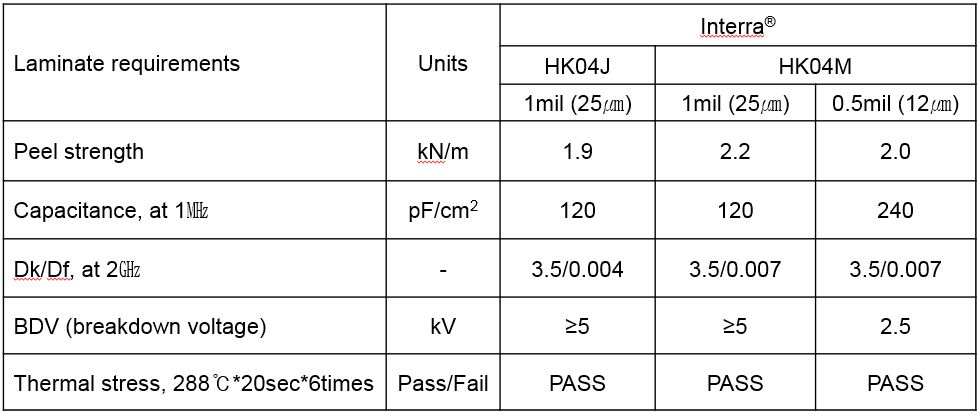

Interra HK04M提供了与HK04J相同的性能优势,进一步改善了机械强度,从而降低了层压板的厚度。Interra HK04M层压板确保了他们在PCB制造过程中提供高质量、性能和稳定性的能力。25µm、12µm HK04M和25µm HK04J的典型层压性能如表1所示。

表1。Interra HK04M层压板的典型性能

Interra HK04M今天有货。杜邦将与客户合作,在他们的新设计中采用HK04M,并优化现有设计。

对于您的PCB制造需求的答案,请单击在这里联系我们的专家。

参考文献

Istvan Novak和Jason R. Miller,配电网的频域特性Artech House, 2007年。

[2] Bill Borland,“基于嵌入式电容技术的高性能半导体解耦”,2006第15届IEEE铁电学应用国际研讨会。

[3] Istvan Novak,“SUN在用于配电的薄层和超薄层板方面的经验”,TechForum TF-THA2, DesignCon 2006。

[4] Istvan Novak,《安静的力量:因果的力量平面模型》PCB设计杂志, 2017年10月。

订阅《创意与创新》

通过提交,您同意我们的隐私政策